AMD下代顯卡殺手鐧:HBM堆疊式3D顯存

2025-05-04 18:49:28 1

2015年5月6日,AMD在紐約召開分析師會議。趁此機會,快科技獨家專訪了AMD事業群首席技術官(Business Unit CTO) Joe Macri,一起聊了聊AMD下代顯卡將首先使用的HBM高帶寬顯存,獲悉了不少新的秘密。

據介紹,AMD從事HBM技術研發已經長達7年了,與包括SK海力士在內的眾多業界夥伴一起完成了這種新一代顯存。AMD方面的負責人是Bryan Black,過去7年的時間他基本都投身在了HBM的研發上,是一位很有勇氣的工程師。

下邊,我們先通過幻燈片了解一下HBM的臺前幕後,在解答一些熱點問題。

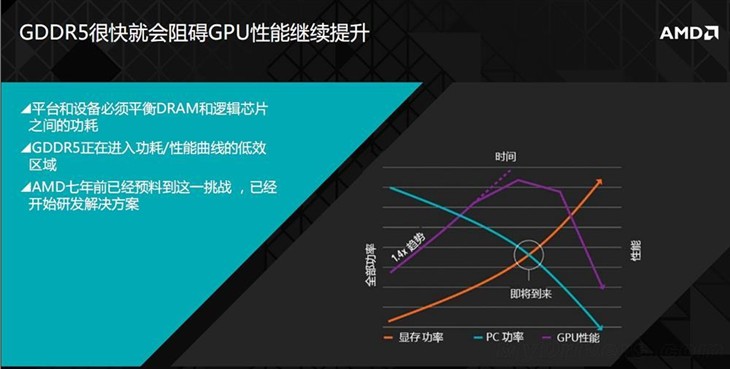

首先是HBM顯存的必要性。目前主流的顯存規格是GDDR5,經過多年的使用和發展已經進入了瓶頸期,迫切需要新的替代技術。

對於任何半導體產品而言,性能和功耗都是一對矛盾體,包括顯卡。如果顯卡整體功耗限定,那麼GPU、顯存兩部分就必須互相妥協,而如今GDDR5顯存的規格越來越高,功耗也水漲船高,導致留給GPU的功耗空間減少,必然影響性能提升。

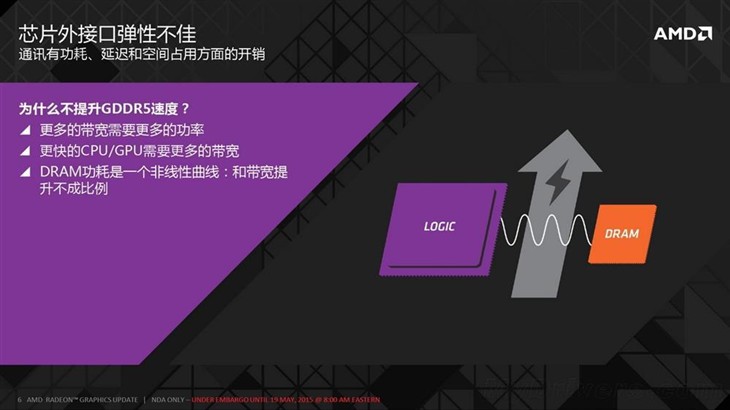

一個關鍵問題就是顯存帶寬,它卻決於顯存的位寬和頻率。位寬都是GPU決定的,太高了會嚴重增大GPU晶片面積和功耗,所以高端顯卡一直停留在384/512位。同時,GDDR5的頻率已經超過7GHz,提升空間不大了。

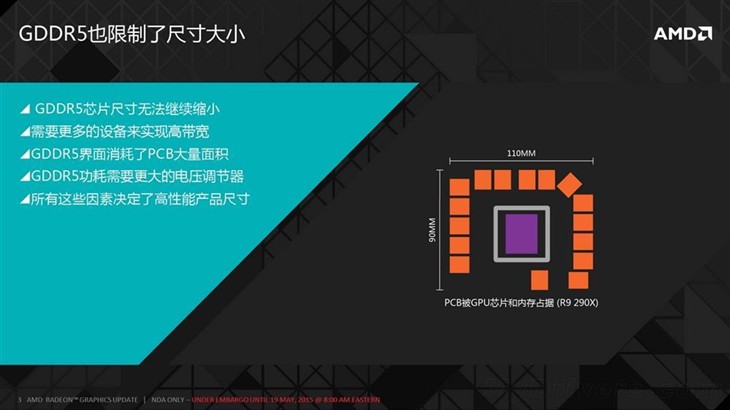

另外,GDDR5(包括以前的顯存)都面臨著「佔地面積」的問題。一大堆顯存顆粒圍繞在GPU晶片周圍,這已經是固定模式,GDDR5再怎麼縮小也無法改變,而且已經不可能再繼續大幅度縮小了。

那麼,將DRAM集成到SoC處理器內部如何呢?目前看得不償失,性能、功耗、尺寸、工藝都是很大的限制,無法獲得足夠的效益,短期內還必須相對獨立。

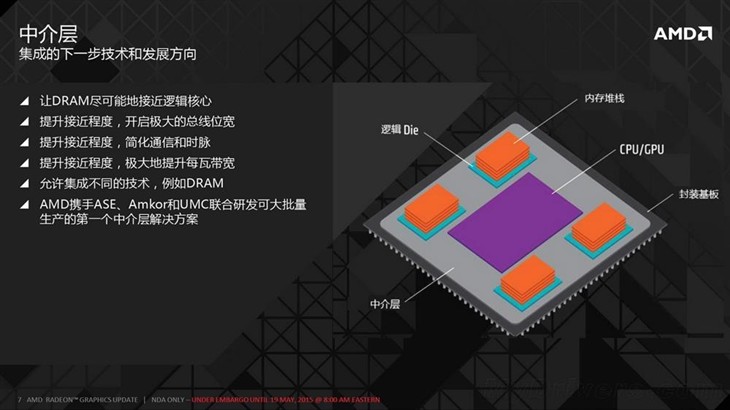

所以合理的下一步解決方案就是「中介層」(Interposer),讓DRAM儘可能接近GPU晶片,封裝在同一基板上,提高通信能力。

於是,AMD聯合ASE、Amkor、聯電等夥伴聯合開發了第一個可以批量生產的中介層方案,用到了HBM顯存上。

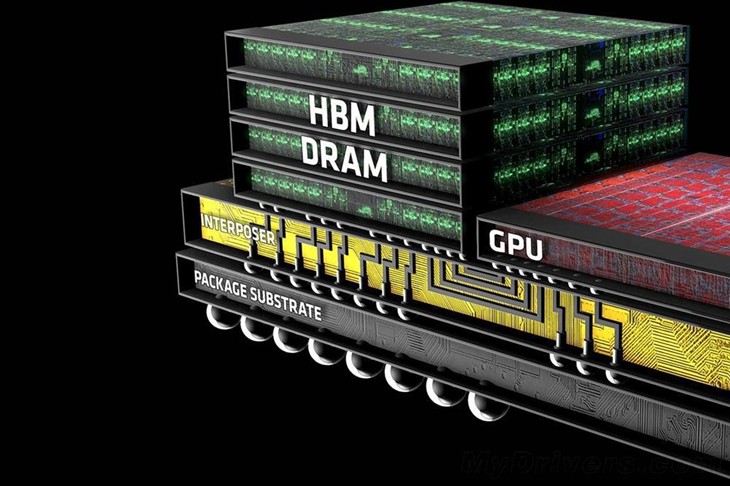

這就是AMD HBM方案的側面剖視圖。這一方案是基於AMD、海力士聯合定義、研發的第一個完整規範和原型。

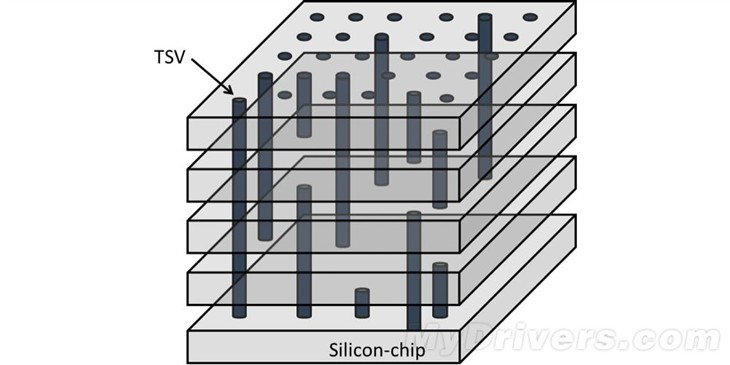

橙色部分就是HBM顯存的Die,3D立體封裝,多個Die(目前最多四個)垂直堆疊在一起,通過TSV矽穿孔和micro-bumps微凸點技術彼此連接。藍色部分是邏輯Die,是一個內外通信接口。

注意,每一個HBM Die都垂直與底部的邏輯Die進行通信,彼此之間是沒有任何聯繫的。

灰色部分是中介層(Interposer),是整個方案的通信員,將HBM顯存與GPU(也可以是CPU/SoC)同構PHY物理層聯繫在一起,同時把它們都固定在封裝基板上。

HBM顯存本身是真正的3D封裝,而整個方案是2.5D封裝。

看這張更有立體感的圖,可以更好地理解HBM的3D結構。

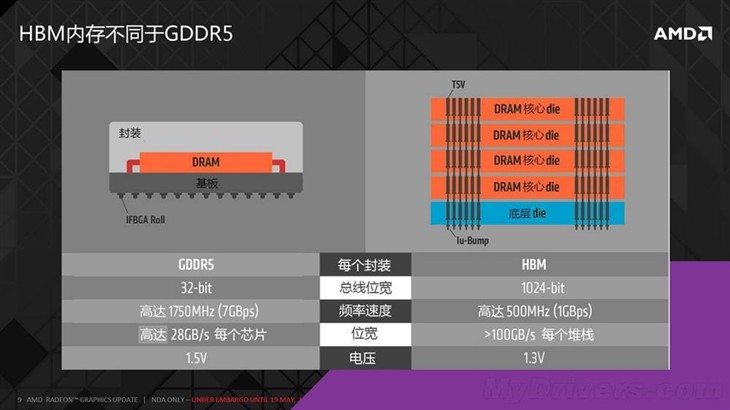

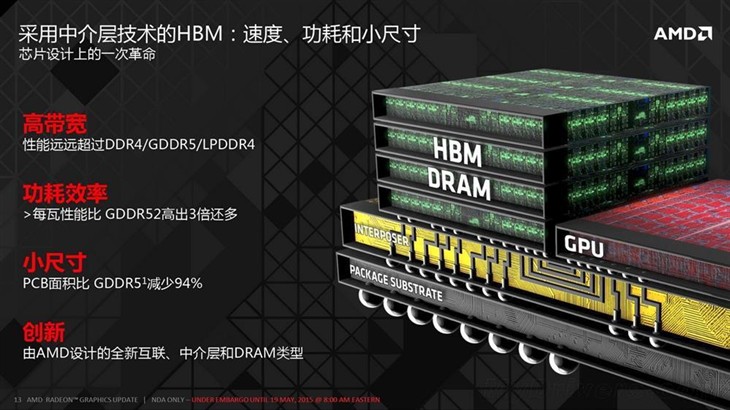

HBM如其名,最大的特點就是高帶寬(確切地說是高位寬),目前已經可以做到單個顆粒1024-bit,GDDR5的足足32倍。顯存帶寬與位寬、頻率都成正比,因此位寬上去了,頻率就不用那麼高了,HBM目前的有效頻率僅僅1GHz,GDDR5的七分之一。

就這樣,HBM每個堆棧的帶寬可以突破100GB/s,GDDR5的四五倍。

更關鍵的是,HBM的電壓要求僅僅1.3V,低於GDDR5 1.5V,更加的節能。

帶寬高了,功耗低了,能效自然非常突出,HBM每瓦特可提供35+GB/s的帶寬,GDDR5則只能勉強超過10GB/s,高下立判。

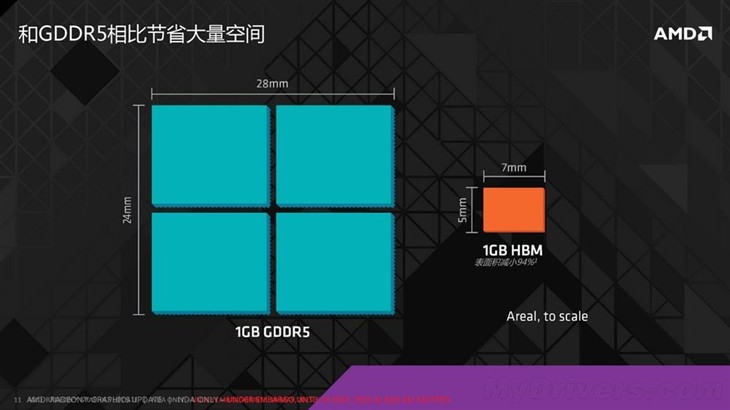

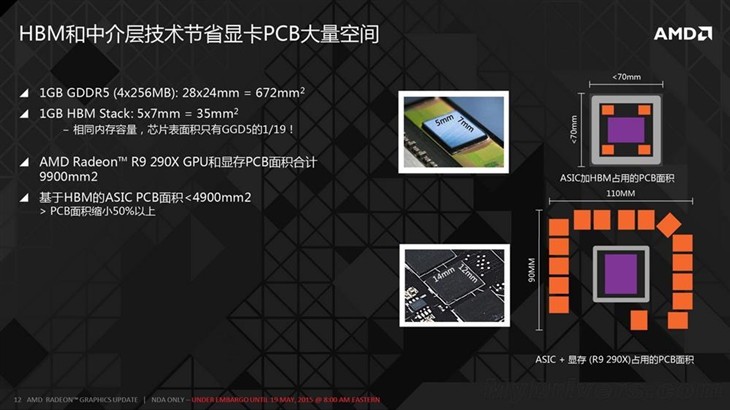

同時,HBM體積小巧,非常節省空間,四層堆疊的1GB HBM只需要5×7=35毫米,而且是圍繞著GPU核心統一封裝,不佔用PCB電路板。

1GB GDDR5則需要24×28=672平方毫米,還得算上封裝針腳,而且都是分布在PCB上的。

因此從GDDR5換到HBM,顯卡的面積可以縮小一半以上。■